OMAPL138EZWTD4 IC MPU OMAP-L1X 456MHZ 361NFBGA

Product Parameter

Description

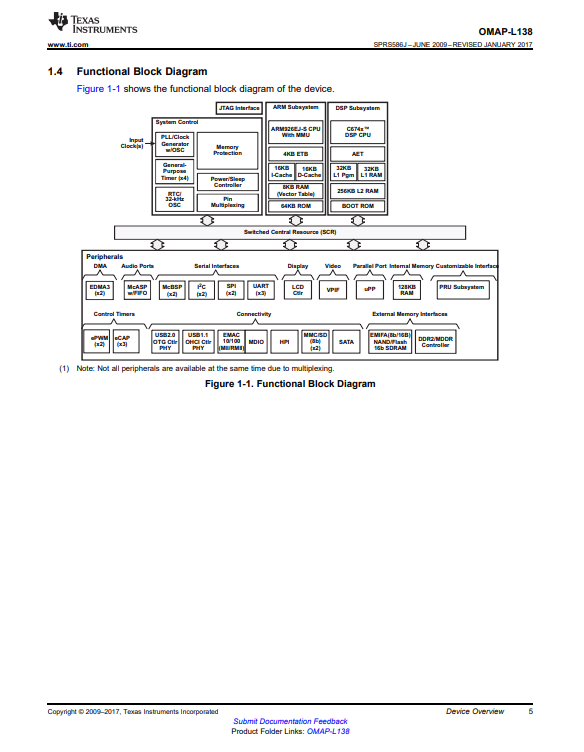

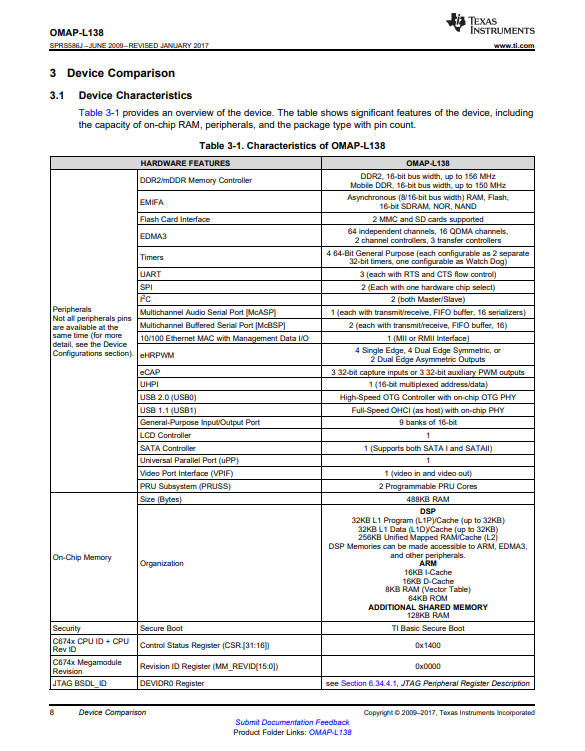

The OMAP-L138 C6000 DSP+ARM processor is a low-power applications processor based on an ARM926EJ-S and a C674x DSP core. This processor provides significantly lower power than other members of the TMS320C6000™ platform of DSPs. The device enables original-equipment manufacturers (OEMs) and original-design manufacturers (ODMs) to quickly bring to market devices with robust operating systems, rich user interfaces, and high processor performance through the maximum flexibility of a fully integrated, mixed processor solution. The dual-core architecture of the device provides benefits of both DSP and reduced instruction set computer (RISC) technologies, incorporating a high-performance TMS320C674x DSP core and an ARM926EJ-S core. The ARM926EJ-S is a 32-bit RISC processor core that performs 32-bit or 16-bit instructions and processes 32-, 16-, or 8-bit data. The core uses pipelining so that all parts of the processor and memory system can operate continuously. The ARM9 core has a coprocessor 15 (CP15), protection module, and data and program memory management units (MMUs) with table look-aside buffers. The ARM9 core has separate 16-KB instruction and 16-KB data caches. Both caches are 4-way associative with virtual index virtual tag (VIVT). The ARM9 core also has 8KB of RAM (Vector Table) and 64KB of ROM. The device DSP core uses a 2-level cache-based architecture. The level 1 program cache (L1P) is a 32- KB direct mapped cache, and the level 1 data cache (L1D) is a 32-KB 2-way, set-associative cache. The level 2 program cache (L2P) consists of a 256-KB memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two. Although the DSP L2 is accessible by the ARM9 and other hosts in the system, an additional 128KB of RAM shared memory is available for use by other hosts without affecting DSP performance.

| Specifications: | |

| Attribute | Value |

| Category | Integrated Circuits (ICs) |

| Embedded - Microprocessors | |

| Mfr | Texas Instruments |

| Series | OMAP-L1x |

| Package | Tray |

| Part Status | Active |

| Core Processor | ARM926EJ-S |

| Number of Cores/Bus Width | 1 Core, 32-Bit |

| Speed | 456MHz |

| Co-Processors/DSP | Signal Processing; C674x, System Control; CP15 |

| RAM Controllers | SDRAM |

| Graphics Acceleration | No |

| Display & Interface Controllers | LCD |

| Ethernet | 10/100Mbps (1) |

| SATA | SATA 3Gbps (1) |

| USB | USB 1.1 + PHY (1), USB 2.0 + PHY (1) |

| Voltage - I/O | 1.8V, 3.3V |

| Operating Temperature | -40°C ~ 90°C (TJ) |

| Security Features | Boot Security, Cryptography |

| Package / Case | 361-LFBGA |

| Supplier Device Package | 361-NFBGA (16x16) |

| Additional Interfaces | HPI, I²C, McASP, McBSP, MMC/SD, SPI, UART |

| Base Product Number | OMAPL138 |

Related PRODUCTS

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp